# 18 Slot PXI Express System

14579-040

# **User Manual**

Release 2.5 03.02.2025

Doc-No: 63972-423

SCHROFF GmbH Langenalber Str. 96-100 75334 Straubenhardt/Germany SCHROFF.nVent.com

|      | -             |                                         |  |

|------|---------------|-----------------------------------------|--|

| R1.0 | July 2019     | Preliminary Release                     |  |

| R1.1 | February 2020 | Manual supplemented                     |  |

| R1.2 | March 2020    | Minor corrections                       |  |

| R1.3 | April 2020    | Front panel added                       |  |

| R1.4 | October 2020  | Technical Update                        |  |

| R1.5 | January 2021  | Clock Specifications added              |  |

| R1.6 | March 2021    | Minor corrections                       |  |

| R1.7 | April 2021    | Updated                                 |  |

| R1.8 | July 2021     | Position of Temperature sensors added   |  |

| R2.0 | May 2022      | Complete Rework. Management description |  |

|      |               | and general information updated.        |  |

| R2.1 | February 2023 | Update Power Supply information due to  |  |

|      |               | change to MEAN WELL NMP1K2              |  |

| R2.2 | July 2023     | Change in PSU parameters due to UL      |  |

|      |               | certification                           |  |

| R2.3 | October 2023  | Correction LED and typos                |  |

| R2.4 | October 2023  | Enhance Operating Temp. up to 55°C      |  |

| R2.5 | June 2024     | Adjusted GND-Connection                 |  |

| R2.6 | January 2025  | UL recognized – E533484                 |  |

|      |               |                                         |  |

Table 1: Revision History

This document is furnished under license and may be used or copied only in accordance with the terms of such license. The content of this manual is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by nVent. nVent assumes no responsibility or liability for any errors or inaccuracies that may appear in this document.

Except as permitted by such license, no part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, manual, recording, or otherwise, without the prior written permission of nVent.

All nVent marks and logos are owned or licensed by nVent Services GmbH or its affiliates. All other trademarks are the property of their respective owners. nVent reserves the right to change specifications without notice.

Copyright © 2022 nVent

All Rights Reserved.

Date: 2025/02/03

Page: 2 of 47

### **Table of Contents**

| 1 Sa  | ıfety                                     | .6 |

|-------|-------------------------------------------|----|

| 1.1   | Intended Use                              | .6 |

| 1.2   | Safety Instructions - Disclaimer          | .6 |

| 1.3   | Safety Symbols                            | .7 |

| 1.4   | Safety Information for Operators          | .7 |

| 2 Re  | eferences and Architecture Specifications | .8 |

| 2.1   | Related Documents                         | .8 |

| 2.2   | Electromagnetic Compatibility             | .8 |

| 2.3   | Safety Certification                      | .8 |

| 2.4   | CE / UKCA Compliance                      | .8 |

| 3 Ge  | eneral Installation                       | .9 |

| 3.1   | Unpacking                                 | .9 |

| 3.2   | Ensuring Proper Airflow                   | .9 |

| 3.3   | Initial Operation                         | .9 |

| 3.4   | Software and Driver Installation1         | 0  |

| 3.5   | SCHROFF System Manager Tool1              | 0  |

| 4 Te  | chnical Information1                      | 1  |

| 4.1   | Technical Data1                           | 1  |

| 4.2   | Key features1                             | 2  |

| 4.3   | Front and Rear View1                      | 3  |

| 4.4   | Signal Architecture1                      | 4  |

| 4.5   | Functional Modules1                       | 5  |

| 4.5.1 | PCIe to PCI Bridge Module1                | 5  |

| 4.5.2 | PCIe 24 Lane Switch1                      | 5  |

| 4.5.3 | Clock Module1                             | 6  |

| 4.5.4 | Trigger Bridge1                           | 6  |

| 4.5.5 | Chassis Management Module1                | 7  |

| 4.6   | Power Supply1                             | 8  |

| 4.6.1 | Available electrical Power1               | 9  |

| 4.6.2       | Maximum Slot Power                          | 19 |

|-------------|---------------------------------------------|----|

| 4.6.3       | Chassis Grounding                           | 20 |

| 4.6.4       | Power-On / Power-Off Behavior               | 21 |

| 4.6.5       | Voltage Monitoring                          | 21 |

| 4.7         | System Cooling                              | 22 |

| 4.7.1       | Air Flow Analysis                           | 23 |

| 4.7.2       | Air Distribution                            | 24 |

| 4.7.3       | Temperature Settings                        | 25 |

| 4.7.4       | Options for limited Installation Conditions | 26 |

| 4.8         | Acoustic Emission                           | 26 |

| 4.9         | Mechanical                                  | 27 |

| 4.9.1       | Materials                                   | 27 |

| 4.9.2       | Dimensions                                  | 27 |

| 5 Sv        | stem Status                                 | 29 |

| <b>5</b> .1 | Indicator LED                               |    |

| 5.2         | Fan Modes                                   |    |

| 5.3         | Power / Inhibit Modes                       |    |

| 5.4         | External Interfaces                         |    |

|             |                                             |    |

|             | ning and Trigger Functions                  |    |

| 6.1         | Trigger and Segments                        |    |

| 6.2         | CLK10, CLK100 parameters                    | 32 |

| 6.3         | Clock Source Selection                      | 33 |

| 6.4         | SYNC_CTRL Behavior                          | 33 |

| 7 SC        | HROFF Chassis Management                    | 34 |

| 7.1         | I2C/SMBus interface description             | 34 |

| 7.2         | I2C Address                                 | 34 |

| 7.3         | Register map:                               | 35 |

| 7.3.1       | Voltage monitor registers                   | 36 |

| 7.3.2       | Power control registers                     | 37 |

| 7.3.3       | Fan control registers                       | 38 |

| 7.3.4                                                                                    | Temperature monitor registers                                                                                                                                                                         |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.3.5                                                                                    | Trigger bridge control registers40                                                                                                                                                                    |

| 7.3.6                                                                                    | Clock control registers41                                                                                                                                                                             |

| 7.3.7                                                                                    | CMM software revision41                                                                                                                                                                               |

| 7.4                                                                                      | Power Management42                                                                                                                                                                                    |

| 7.4.1                                                                                    | SEL_SS_PS_ON (select PS_ON input source)42                                                                                                                                                            |

| 7.4.2                                                                                    | SS_PS_ON_IN (system slot PS_ON input)42                                                                                                                                                               |

| 7.4.3                                                                                    | EXT_PS_ON_IN (external PS_ON input)42                                                                                                                                                                 |

| 7.4.4                                                                                    | PS_ON_OUT_X (X = [1:4])42                                                                                                                                                                             |

| 7.4.5                                                                                    | PWR_OK43                                                                                                                                                                                              |

|                                                                                          |                                                                                                                                                                                                       |

| 8 Se                                                                                     | rvice44                                                                                                                                                                                               |

| <b>8 Se</b><br>8.1                                                                       | <b>rvice44</b><br>Technical support and Return for Service Assistance44                                                                                                                               |

| 8.1                                                                                      |                                                                                                                                                                                                       |

| 8.1                                                                                      | Technical support and Return for Service Assistance44                                                                                                                                                 |

| 8.1<br>8.2<br>8.3                                                                        | Technical support and Return for Service Assistance                                                                                                                                                   |

| 8.1<br>8.2<br>8.3<br>8.4                                                                 | Technical support and Return for Service Assistance                                                                                                                                                   |

| 8.1<br>8.2<br>8.3<br>8.4                                                                 | Technical support and Return for Service Assistance                                                                                                                                                   |

| <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>8.6</li> </ul> | Technical support and Return for Service Assistance       .44         Warranty       .44         Disposal       .44         Scope of Delivery       .45         Accessories and Spare Parts       .45 |

## 1 Safety

### 1.1 Intended Use

The nVent SCHROFF PXIe System 14579-040 described in this manual is a high performance 18-slot PXI Express chassis based on an allover fundamental modular design. The following description of included features and installation guideline shall support a wide range of application cases. Intended use includes compliance with the terms and conditions for assembly, disassembly, commissioning, operation and maintenance, specified by the manufacturer. The PXIe System is only intended for use in dry and dust-free locations, i.e. indoors, in an industrial environment or for commercial use. If the equipment is used in a manner not specified by the manufacturer, the protection provided by the equipment may be impaired.

### 1.2 Safety Instructions - Disclaimer

nVent SCHROFF accepts no liability for any errors in this documentation. To the maximum extent permissible by law, any liability for damage, direct or indirect, arising from the supply or use of this documentation is excluded.

nVent SCHROFF retains the right to modify this document, including the liability disclaimer, at any time without notice and accepts no liability for any consequences of such alterations.

#### 1.3 Safety Symbols

In these original operating instructions, warning notices point out residual risks that cannot be avoided by constructive means when installing or operating the PXIe System. The warning notices are classified according to severity of the damage occurring and its statistic occurrence.

|        | Short description of the danger                         |  |  |

|--------|---------------------------------------------------------|--|--|

| Symbol | The signal word DANGER indicates an immediate danger.   |  |  |

|        | Non-observance will result in severe injuries or death. |  |  |

|        | Short description of the danger                      |  |  |  |

|--------|------------------------------------------------------|--|--|--|

| Symbol | The signal word WARNING indicates a possible danger. |  |  |  |

|        | Non-observance can lead to serious injury or death.  |  |  |  |

| ⚠ | CAUTION |  |

|---|---------|--|

|---|---------|--|

| Short description of the danger |        |                                                      |

|---------------------------------|--------|------------------------------------------------------|

|                                 | Symbol | The signal word CAUTION indicates a possible danger. |

|                                 |        | Non-observance can lead to injuries.                 |

# ATTENTION

#### Short description

The signal word ATTENTION indicates possible damages to equipment. Non-observance can lead to damage to the device.

### Important information

### 1.4 Safety Information for Operators

Only trained specialists are authorized to carry out assembly, commissioning, completion, maintenance and service of the PXIe System. The nationally applicable health and safety regulations must be adhered as well.

#

Risk of injury due to insufficient personal protective equipment

If you use wrong / no protective equipment at all, serious injuries are possible. - Wear protective equipment adapted to the work processes.

- Check the protective equipment before each use to ensure that it is intact!

- Use only approved protective equipment.

# 2 References and Architecture Specifications

#### 2.1 Related Documents

This product meets the requirements of the following specifications:

- IEEE 1101.1-199, including IEC 603-2 Connectors

- IEEE 1101.10, including IEEE 1101.1 Equipment Practice,

- ATX Specification Version 2.4

- PICMG EXP.0 Revision 2.0 CompactPCI Express Specification

- PICMG 2.0 R3.0 CompactPCI Specification

- PXI-1 Hardware Specification Rev 2.3

- PXI-2 Software Specification Rev 2.4

- PXI-5 PXI Express Hardware Specification Rev 2.0

#### 2.2 Electromagnetic Compatibility

The requirements of the following EMC standards for electrical equipment are fulfilled and verified via an independent EMC test laboratory.

- EN 61326-1 class B group 1

- EN 61000-3-3

Basic Immunity Limitation of voltage changes, voltage fluctuations and flicker Limits for harmonic current emissions

EN 61000-3-2 Limits for I

EN 55011 (CISPR11), EN 55022 (CISPR 22) and EN 55024 (CISPR 24) are implied and in fact fulfilled by EN 61326-1. The international standards AS/NZS (CISPR 11) and AS/NZS (CISPR 22) are also implied by EN 61326-1 and basically fulfilled.

#### 2.3 Safety Certification

•

The product is designed to meet the requirements of the following electrical equipment safety standards for measurement, control and laboratory use.

• EN 61010-1 / IEC 61010-1

#### 2.4 CE / UKCA Compliance

Essential requirements of applicable European Directives are met by this product. Since 2020 the UKCA declaration requirements are fulfilled as well.

- LVD 2014/35/EU Low-Voltage Directive

- EMC 2014/30/EU

- Electromagnetic Compatibility Directive

- RoHS 2011/65/EU

- RoHS Directive 2

Products fulfilling those requirements are marked with a CE/UKCA label.

For Declarations of Conformity of this product please visit <u>https://SCHROFF.nvent.com/</u>

# **3** General Installation

#### 3.1 Unpacking

# ATTENTION

When opening the shipping carton, use caution to avoid damaging the system.

Consider the following when unpacking and storing the system:

- · Leave the system packed until it is needed for immediate installation.

- After unpacking the system, save and store the packaging material in case the system must be returned.

If the packaging is damaged and possible system damage is present, report to the shipper and analyze the damage.

#### 3.2 Ensuring Proper Airflow

- Maintain ambient airflow to ensure normal operation. If the airflow is blocked or restricted, or if the intake air is too warm, an overtemperature condition can occur.

- Ensure that cables from other equipment do not obstruct the airflow through the system.

- Use the filler panels (included in the delivery) to cover all empty chassis slots. The filler panel prevents air entering at front of an open slot and improves airflow distribution across the chassis

- If necessary, use air baffles (available as accessories) to prevent air short circuits in unused slots.

#### 3.3 Initial Operation

#

**Risk of injury and accidents due to insufficiently qualified personnel!** The installation may only be carried out by qualified personnel who are authorized to do so according to the valid safety regulations, e.g. by authorized specialized companies or authorized departments of the company.

- Ensure that the system has not been damaged during transport, storage or assembly

- Check the Protective Earth (PE) resistance, should be < 0,1 Ohm

- Plug-in the system controller and peripheral boards

- Ensure that all open slots are covered with filler panels or even air baffles

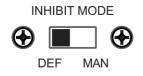

- Ensure that the switch **INHIBIT MODE** at the rear side is set to **DEF**

- Ensure that the switch **FAN SPEED** at the rear side is set to **AUTO**

- Ensure rear AC main switch is set to off ("O")

- Connect the power cable and switch on the mains/line switch at the power input

- Push the power button at the front side to switch on the system

#### 3.4 Software and Driver Installation

Parametric information of nVent SCHROFF PXI Express chassis is included in a *chassis.ini* description file. Together with EEPROM stored data the used system controller creates a *pxisys.ini* file for the PXI system initialization within OS environment. For the creation of that file the used controller uses PXI-6 dedicated drivers. A complete software package (*PXIe\_Initial\_Setup*) with essential drivers, ini. files and registry settings is available under following address <u>https://SCHROFF.nvent.com/en-de/products/enc14579-040</u>

#### 3.5 SCHROFF System Manager Tool

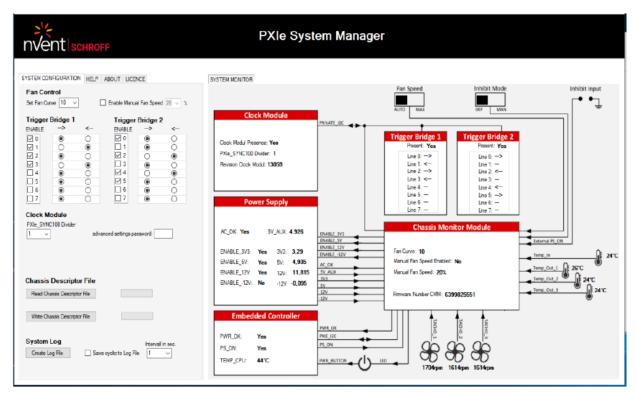

nVent SCHROFF PXI Express systems can be displayed and managed by the tool **SCHROFF PXIe System Manager**. With the system manager tool all featured chassis functions can be monitored and controlled. For general direct access to chassis management registers all controller based I2C/SMBus interfaces, featured in PXI-6, can be used as well. The registers are described in detail under chapter <u>7 Chassis Management</u>. For further technical questions please get in contact with your local sales representative.

Figure 1: Screenshot PXIe System Manager

# 4 Technical Information

#### 4.1 Technical Data

The following table provides general product information of the nVent SCHROFF 14579-040.

#### Table 2: Technical Data

| Dimension                      | S                            |                                                                                |  |  |

|--------------------------------|------------------------------|--------------------------------------------------------------------------------|--|--|

| Height (w/o feet)              |                              | 177 mm (4 U)                                                                   |  |  |

| Height (with feet)             |                              | 192 mm                                                                         |  |  |

| Width (with mounting brackets) |                              | 84 HP (19"/ 482.6 mm)                                                          |  |  |

| Depth (Ove                     | rall w/o handles)            | 355.25 mm                                                                      |  |  |

| Weight                         |                              |                                                                                |  |  |

| System with                    | nout cards and filler panels | 9,9 kg                                                                         |  |  |

| Power Sup                      | ply                          |                                                                                |  |  |

| Input Voltag                   | le                           | 100 VAC to 240 VAC (IEC 60320-C14)                                             |  |  |

| Main Supply                    | y Voltage fluctuations       | 10%                                                                            |  |  |

| Overvoltage                    | e category                   | II                                                                             |  |  |

| Frequency (                    | (nom / operating)            | 50/60 Hz                                                                       |  |  |

| Power input                    | :                            | up to 1200 VA                                                                  |  |  |

| Efficiency                     |                              | up to 91.5% (full load case)                                                   |  |  |

| Over-curren                    | It protection                | Fuse 8 A slow blow (T8AH250V)                                                  |  |  |

| Ambient                        |                              |                                                                                |  |  |

| Operation                      |                              | +0 °C to +55 °C                                                                |  |  |

| Storage                        |                              | -40 °C to +85 °C                                                               |  |  |

| Admissible humidity            |                              | 20 % to 80 %, non-condensing, 2000m                                            |  |  |

| Pollution de                   | gree                         | 2                                                                              |  |  |

| Shock and                      | Vibration                    |                                                                                |  |  |

| Shock                          |                              | 15 g peak, 11 ms halfsine EN 60068-2-27                                        |  |  |

| Vibration                      | operation<br>non-operation   | 5 to 100 Hz, 0,15 g rms EN 60068-2-64<br>5 to 500 Hz, 1,87 g rms EN 60068-2-64 |  |  |

| EMC:                           |                              |                                                                                |  |  |

| EMC                            |                              | EN 61326-1 class B group 1<br>EN 61000-3-3<br>EN 61000-3-2                     |  |  |

| Safety                         |                              |                                                                                |  |  |

| Safety                         |                              | EN 61010-1 / IEC 61010-1<br>UL recognized – E533484                            |  |  |

#### 4.2 Key features

The nVent SCHROFF PXI Express chassis 14579-040 is designed for high performance applications and supports a wide range of requirements due to its modular base structure. The well balanced combination of a performant, configurable 1200W power supply, the high bandwidth PCI Express switch architecture and the full PXI-1/CPCI downwards compatibility combined with access to all featured chassis functionalities provides customers a platform for the highest demands and usability. The nVent SCHROFF PXIe Chassis meets the highest quality requirements for advanced timing, synchronization and trigger signals.

The underlying modular design impresses with high quality due to deeply verified standard function modules and enables the customer to operate a system with lowest failure rate and high maintainability.

- Shielded 4 U SCHROFF ratiopacPRO-air case with mounting brackets for 19" rack mounting, front handles and tip-up feet for desktop use

- 84 HP / 18 slot front card cage for 3 U boards

- compatible for PXI-5 as well as PXI-1, CompactPCI and CompactPCI Express modules

- 18 slot 3 U backplane containing:

- 1 PXIe system slot, 4 16 HP

- 1 PXIe timing slot, 4 HP

- 16 PXI Express Hybrid slots, 4 HP

- System Bandwidth up to 16 GB/s (4 x4 Port Configuration)

- Up to 4 GB/s (single direction) per PXI Express slot dedicated bandwidth (x4 Gen-3 PCI Express) grouped within four PCIe switch segments

- BNC connectors for 10 MHz clock input/output at the rear side

- High Accuracy / Low Jitter Performance for CLK10, CLK100, SYNC100 signals with featured SYNC\_CTRL functions

- PXI\_STAR and PXIe\_DSTAR[A:C] signals matched in propagation delay to all slots

- Integrated power supply (1200 W) with wide range input

- Power input module with IEC 60320-C14 connector containing mains/line switch, mains/line filter and fuses

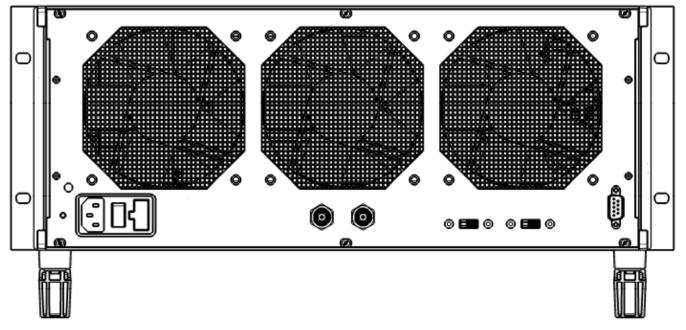

- 3x 120 mm Fans for active cooling controlled and monitored by the Chassis Management

- Push Button with chassis status indicator LED at front side

This user manual describes features and system characteristics of the 14579-040 system. The technical description may also apply to customer-specific systems that are based on this manual.

#### 4.3 Front and Rear View

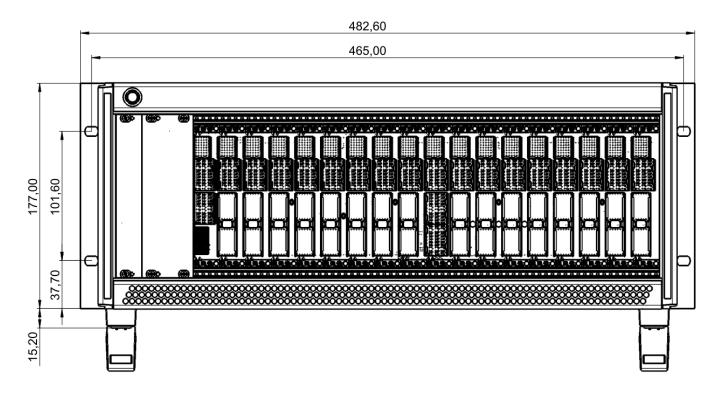

The 4U case is based on the nVent SCHROFF ratiopacPRO-air system with EMC shielding. The 3 U card cage provides 1 system slot (4- 16 HP), 1 timing slot (4 HP) and 16 peripheral slots (4 HP). The lower guide rails of the card cage are equipped with ESD clips. Figure 2: Front and Rear View

| 1 | Push Button with Status Indication LED    | 7  | VMON Connector, DSUB-9          |

|---|-------------------------------------------|----|---------------------------------|

| 2 | Filler Panels 4/8HP System Slot Extension | 8  | CLK10_IN / _OUT Connectors, BNC |

| 3 | PXIe Slots for Card Insertion             | 9  | Fans / Air Outlet               |

| 4 | Air Intake                                | 10 | Fan Mode Slide Switch           |

| 5 | Power Input Module, IEC 60320-C14         | 11 | Power Mode Slide Switch         |

| 6 | Grounding stud (M5)                       |    | ۱<br>۱                          |

#### 4.4 Signal Architecture

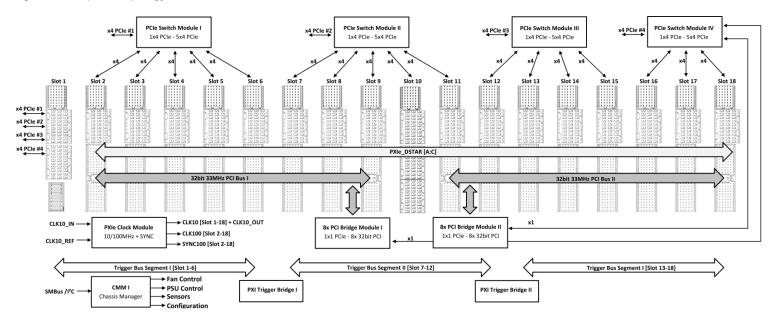

The PXI Express system and backplane provides following slots and signal architecture:

• PXI Express System Controller Slot (Slot 1)

The System Slot is a 4 port (4 x4 Gen3) configured host interface for the usage of PXI Express and Compact PCI Express based controller or adapter cards. The System Controller can have a physical width between 4-16 HP. Each x4 Gen3 PCIe port of the System slot is connected to a PCI Express switch fabric module distributing PCI Express to the peripheral segments. The max. bandwidth (single direction) is up to 16GB/s in total and 4GB/s to each Switch peripheral segment. In addition the switch inner segmental bandwidth is optimized for clustered applications due to flexible packet flow control and does not affect the upstream / CPU performance.

#### PXI Express System Timing Slot (Slot 10)

The System Timing Slot can either be used with an CPCIExpress / PXI Express Peripheral Card or and a dedicated PXI Express System Timing Module up to x4 Gen3 PCI Express. When the PXI\_CLK10\_TS pin of the timing slot is used, the linked to clock module will be phase locked and use the System Timing Slot as reference for enhanced clock quality or synchronization. The PXI\_STAR and DSTAR signal groups are all matched in propagation delay and connected in star-shape to all slots according to PXI-5.

• PXI Express Hybrid Peripheral Slots (16x Slots, Slot 2-9 and 11-18)

The 16x PXI Express Hybrid Slots are supported with x4 Gen3 PCI Express Links with up to maximum bandwidth of 4 GB/s single direction and with a 32bit 33MHz PCI Bus segment connection. The peripheral slots are physically accepting CompactPCI, PXI-1, CompactPCI Express, and PXI Express Peripheral Cards and are providing full PXI Express functionality, as well as the PXI Local Bus.

#### Figure 3: Backplane Topology

#### 4.5 Functional Modules

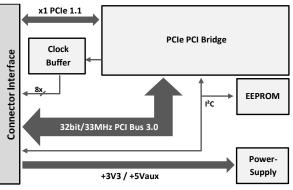

#### 4.5.1 PCIe to PCI Bridge Module

The nVent SCHROFF PCIe-to-PCI Bridge is a high performance bridge designed in accordance to the PCI Express-to-PCI Bridge Specification 1.1 enabling applications to migrate legacy parallel PCI bus interfaces to the advanced serial PCI Express. The bridge module is equipped with a single lane PCI Express port and a parallel bus segment supporting the conventional PCI operation for up to eight PCI peripheral devices concurrently.

Figure 4: PCIe to PCI Bridge Module

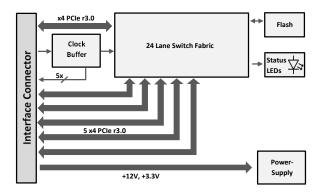

#### 4.5.2 PCIe 24 Lane Switch

The nVent SCHROFF PCIe Switch is a 24-lane, 6-port, PCIe Gen 3 switch device that enables users to connect a PCI Express host to respective endpoints via a fully transparent, high-bandwidth, non- blocking peer-to-peer interface. The default configuration with a x4 Gen3 PCI Express upstream port to the host supports up to five x4 Gen3 downstream clients. For further information (e.g. custom configuration) or SI reports feel free to contact your local sales partner.

Port Configuration: Compatibility: 1 x4 upstream, 5 x4 downstream PCI Express Gen3 PCI Express Base Specification R3.0, PCI Express Base Specification R2.0, PCI Express Base Specification R1.0a/1.1

Figure 5: PCIe 24 Lane Switch Module

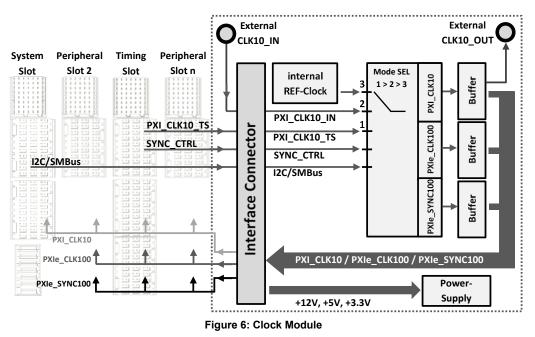

#### 4.5.3 Clock Module

According to PXI-1 and PXI-5 specification, the nVent SCHROFF PXIe system provides time correlated signal groups PXI\_CLK10 and PXIe\_CLK100 / PXIe\_SYNC100. PXI\_CLK10\_OUT is also attached to an external BNC connector 10 MHz REF OUT at the chassis rear side.

Clock source selection, signal generation and all timing correlations are managed by an clock module, described in the shown block diagram. When a 10 MHz reference clock is present at the System Timing Slot or the external panel connector CLK10\_IN, PXI\_CLK10, PXIe\_CLK100 and PXIe\_SYNC100 are phase-locked to this reference clock signal according to chapter 6.3.

### 4.5.4 Trigger Bridge

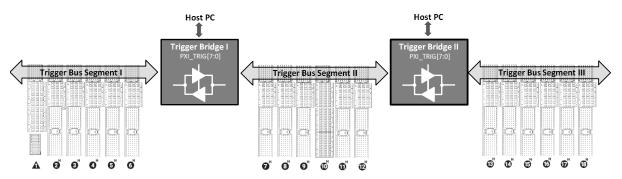

For best signal behaviors and low bus capacity a trigger bus shall be limited for up to eight trigger devices according to PXI-1. Trigger buses exceeding slot counts are divided into several individual trigger segments and can be connected unidirectional into both directions via trigger bridges. Trigger bridges are configured by the Host PC or direct I2C/SMBus access. Upon power cycle the last valid trigger configuration is reloaded by the trigger bridge.

Each segment is fully terminated on both ends for optimized trigger performance, even external trigger feed in/out is possible with custom trigger bridge architecture. For further information (e.g. custom configuration) or SI reports feel free to contact your local sales partner.

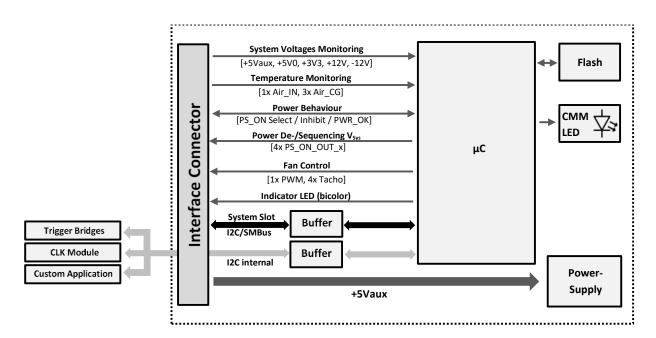

#### 4.5.5 Chassis Management Module

The Chassis Management Module (CMM) is dedicated to manage all functions of the chassis. The block diagram below shows the management architecture of the PXIe chassis. The CMM provides access to voltage monitor, FAN settings, temperature monitor, Trigger bridge settings and PXIE\_SYNC100 frequency settings. The status of chassis functions can be monitored/changed by access corresponding CMM register settings. The System module connects to the CMM via I2C/SMBus which allows access to its configurable registers from the host operating system. However, it is not necessary to access the CMM in default operation. Upon first use it acts autonomously and can be changed in its behavior if required.

Figure 8: Chassis Management Module (CMM)

#### 4.6 Power Supply

# A DANGER

Danger of electric shock

Danger of overheating

Parts of the power supply may be exposed with hazardous voltage. Always remove mains/line connector before carry out any assembly work.

# **A** CAUTION

Your system has not been provided with a AC power cable. Purchase an AC power cable that is approved for use in your country. The AC power cable must be rated for the product and for the voltage and current marked on the product's electrical ratings label. The voltage and current rating of the cable should be greater than the ratings marked on the product.

The PXI Express system 14579-040 is powered by a high efficiency modular 1200 W power supply with wide range AC input.

#### Table 3: Input and Output Voltages

| Input voltage nominal | 100 - 240 V  | 100 - 240 VAC |           |         |  |  |

|-----------------------|--------------|---------------|-----------|---------|--|--|

| Mains Frequency       | 50 / 60 Hz / | 400Hz         |           |         |  |  |

| Power (max. combined) | 960 W        |               |           |         |  |  |

| System Voltages       | Voltage      | Current       | Load Reg. | Ripple  |  |  |

|                       | +3.3 V       | 72 A          | ±2 %      | ±50 mV  |  |  |

|                       | +5.0 V       | 36 A          | ±2 %      | ±50 mV  |  |  |

|                       | +5.0 Vaux    | 2 A           | -         | ±50 mV  |  |  |

|                       | +12.0 V      | 40 A          | ±2 %      | ±100 mV |  |  |

|                       | -12.0 V      | 5 A           | ±2 %      | ±100 mV |  |  |

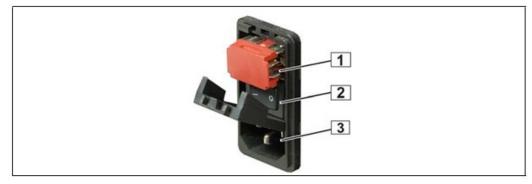

An AC mains/line module provides the power input with IEC 60320-C14 connector, integrated mains/line fuses and line filter. The fuse rating is 8 A slow blow (T8AH250V).

### Figure 9: AC mains/line module 3 AC Cor

1 Fuse holder

AC Connector (IEC60320-C14)

2 Mains/line switch

#### 4.6.1 Available electrical Power

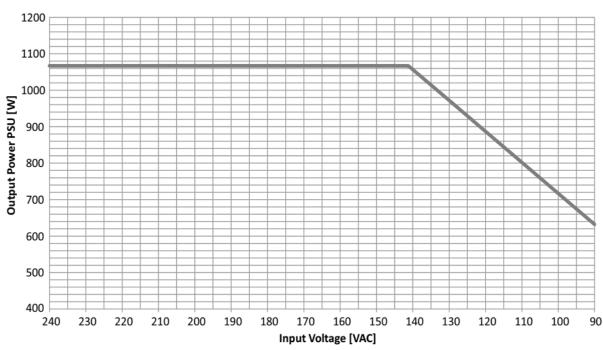

The input current of the chassis is limited to 8 A. This results in an available PSU output power at the following nominal AC input voltages:

| The power for the fans and internal chassis function modules is already |               |                                 |  |  |  |

|-------------------------------------------------------------------------|---------------|---------------------------------|--|--|--|

| deducted in                                                             | the cald      | culation and the diagram below. |  |  |  |

| 100 VAC                                                                 | $\rightarrow$ | 700 W                           |  |  |  |

| 115 VAC                                                                 | $\rightarrow$ | 800 W                           |  |  |  |

| 230 VAC                                                                 | $\rightarrow$ | 960 W                           |  |  |  |

**Derating Output Power PSU**

Figure 10: Output Power Derating

#### 4.6.2 Maximum Slot Power

The table below shows the maximum available current per voltage per slot type. Limiting factors are the maximum current per connector, overall load distribution and available cooling depending on the installed board air impedance and electrical power.

#### Please note:

- All current carrying backplane pins must be used by the boards

- The cooling capacity of the PXIe chassis for max. 50 W peripheral cards please refer to <u>chapter 4.7.2</u> for more detail

- Max. PSU power for different AC input levels

Table 4: Maximum Slot Current Capability

#### Fehler! Keine gültige Verknüpfung.

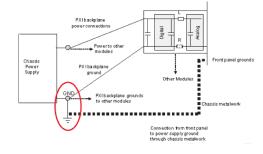

#### 4.6.3 Chassis Grounding

The unit is designed in accordance with IEC320 protection class 1! It must therefore be operated with protective earth/GND connection. Use only a three conductor AC power cable with a protective earth conductor that

meets the IEC safety standards!

The PXI Express system provides an additional ground terminal at the rear side panel. If necessary, an additional protective ground cable can be connected to the bolt. Please make sure that an appropriate sized cable cross-section is used for this purpose.

According to PXI-1 Hardware Specification Rev 2.3 chapter 4.4 Signal Logic GND and Chassis GND (PE) are connected via Backplane assembly points. It is possible to isolate Logic GND from chassis potential with a different type of washer. For more information get in contact with your local sales representative.

#### 4.6.4 Power-On / Power-Off Behavior

When the chassis power mode switch is set to "**DEF**", the Chassis Management controls the power supply inhibit, which means, the chassis can be powered on and off by pushing the power button at the left front side. When the inhibit mode switch is set to 'MAN', the chassis boots when AC-power is applied, as long as Pin 5 at the DSUB connector is not connected to GND. During Power-On and -Off DC voltages are de-/sequenced, see <u>7.4.5</u>.

#### 4.6.5 Voltage Monitoring

Voltages are measured and controlled by chassis management and can be accessed by the rear DSUB, see <u>5.4</u>. When the measured system voltages are exceeding the 5% tolerance according to ATX specification for >1 sec the system will provide DC shutdown and the LED will be flashing red, see <u>5.1</u>.

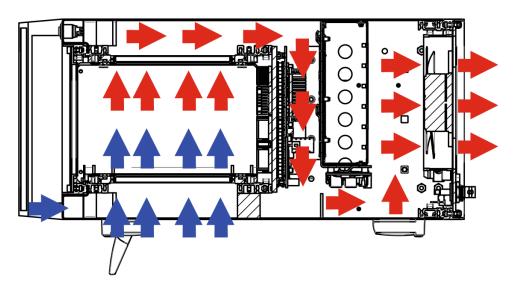

### 4.7 System Cooling

The PXIe boards are cooled by forced air convection with three controlled 12 VDC axial fans. The air enters the subrack at the perforated bottom panel into the bottom air plenum. As the air passes across the hot components on the peripheral Boards, heat is carried away by forced convection. The air exits the cardcage at the top, is drawn into the upper plenum, turns 90°, passes the modules located at the backplane's rear side and is exhausted out the rear of the chassis by three fans. The cooling capacity of the PXIe chassis can handle 50 W peripheral cards. For more details to air distribution and cooling capacity, please refer to <u>chapter 4.7.2</u>. The actual heat dissipation for a specific slot depends on the pressure drop of the card used and the occupancy of the adjacent slots. For high performance cards, the slot with the highest air flow should be used and the air flow (see Fig. 12) of adjacent slots should be reduced by air baffles.

For more powerful applications, higher performance fans can easily be used for a customized configuration. Up to 80W per slot are possible at this point. Please contact your local sales partner for more information.

# ATTENTION

#### Danger of Overheating

To maintain proper airflow, all open slots must be covered with filler panels. The filler panel should include an airflow baffle that extends to backplane.

For desktop use, unfold the front tip-up feet for optimal cooling efficiency.

For rack mounting, at least 1 U (44.5 mm/1.75 in.) clearance below the chassis is required.

Figure 11: Air Flow

#### 4.7.1 Air Flow Analysis

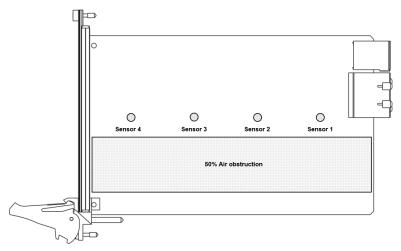

The following air flow analysis performed with the test system 14579-040 and the nVent SCHROFF air performance test setup. Air flow measurement of the 18-Slot PXIe (14579-040) was performed @ 100%, 90%, 80%, 70%, 60%, 50%, 40% and 30% fan speed. The PXIe system was fixed at an air performance test rig. During the test procedure the system was equipped with dummy impedance boards to simulate real chassis setup conditions. These Dummy Impedance Boards consists of a PCB with an obstruction on the top side, which is defined for an 50% air blockage within the 4TE wide air channel.

Figure 12: Dummy Impedance Board

The value of 50% is empiric and varies under real application conditions in accordance to the used peripheral cards into uneven populated blockage setup with more or less blockage at each slot. The following measurements shall be used as a well evaluated data base for further integration considerations. For more detailed information to air flow measurements or optional fine tuning options for your chassis please get into contact with your local sales partner.

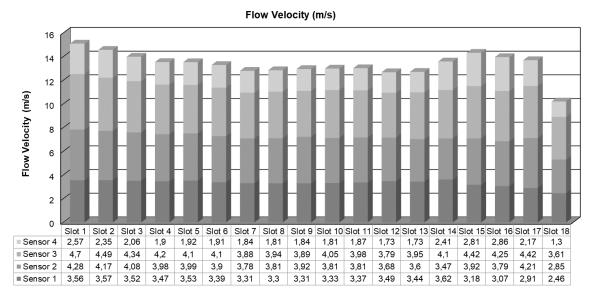

#### 4.7.2 Air Distribution

All measured sensor air flow is summed up and used as per slot air velocity. As there are only four measurement points overall, accuracy has to be set in correlation with the total air flow measured by air performance test bench.

The assigned slot cooling power is defined on max. 15K temperature increase (in --> out).

| slot                                                      | 1          | 2     | 3     | 4             | 5            | 6      | 7        | 8     | 9     | 10    | 11    | 12    | 13    | 14    | 15    | 16    | 17    | 18    |

|-----------------------------------------------------------|------------|-------|-------|---------------|--------------|--------|----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| air flow [m3/h]                                           | 11,54      | 11,14 | 10,69 | 10,35         | 10,34        | 10,16  | 9,78     | 9,93  | 9,90  | 9,93  | 9,95  | 9,69  | 9,71  | 10,39 | 10,94 | 10,67 | 10,47 | 7,81  |

| cooling capacity* [W]                                     | 52,46      | 50,62 | 48,60 | 47,04         | 47,00        | 46,17  | 44,47    | 45,13 | 44,99 | 45,13 | 45,23 | 44,05 | 44,16 | 47,21 | 49,75 | 48,50 | 47,59 | 35,48 |

| *∆T = 15K                                                 | * ΔT = 15K |       |       |               |              |        |          |       |       |       |       |       |       |       |       |       |       |       |

| air volume flow slot 1-18 183,39 m³/h                     |            |       |       | m³/h          |              |        |          |       |       |       |       |       |       |       |       |       |       |       |

| air volume flow of free expansion slots                   |            |       |       | 28,45         | m³/h         |        |          |       |       |       |       |       |       |       |       |       |       |       |

| total air volume flow air performance test bench meausred |            |       |       | 211,84<br>218 | m³/h<br>m³/h | 2,83 % | deviatio | n     |       |       |       |       |       |       |       |       |       |       |

Figure 13: Air Distribution

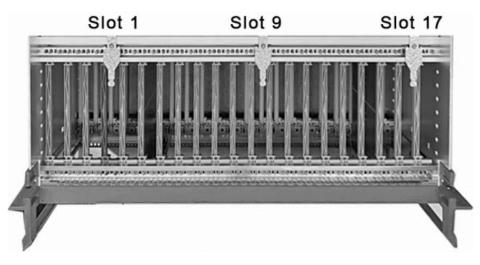

#### 4.7.3 Temperature Settings

Figure 14: Temperature Sensors

3 NTC temperature sensors located in top of the card cage are monitored by the chassis management. The highest temperature level is the referred control parameter for the overall fan speed.

To ensure proper fan control, place the PXIe Modules with the highest heat dissipation in the slots directly underneath the NTC temperature sensors (Slot 1, 9, 17).

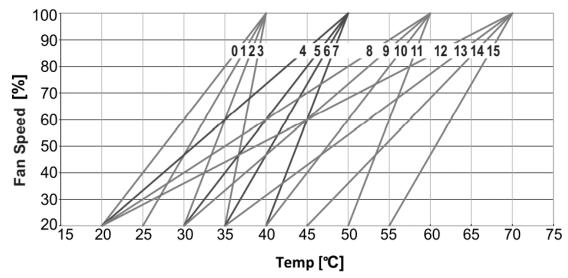

The fan speed is controlled by the chassis management depending on a fan level control curve. 16 fan control curves are available and can be selected by the chassis management via host or can be directly written via I2C/SMBus. The default fan curve is "5". A manual fan speed control or max. fan level via rear switch is also possible.

For more information, see chapter 7.3.3 Fan Control register or 5.2 Fan Modes.

Figure 15: Fan Curves

#### 4.7.4 Options for limited Installation Conditions

For general operation the requirements in <u>chapter 3.2</u> must be fulfilled. If the installation environment does not correspond to that, general operation of the chassis is also possible for limited conditions **with reduced cooling capacity per slot**. In this case the 4U chassis can be operated with a fully blocked bottom air inlet perforation. Please make sure that the lower front air entrance and rear air outlet is free of obstacles. Within this limited conditions an average cooling capacity of about **20W / slot** (with  $\Delta T = 15K$ ) can be assumed without any further airflow restrictions.

If there is no need for such limited condition, we highly recommend the operation under <u>3.2</u> stated conditions for best performance.

For further evaluated simulation information or application guidance get into contact with your local sales partner.

#### 4.8 Acoustic Emission

The accoustic emission test was performed under the condition that the PXIe chassis was placed on the test desk. The sound intensity measurement was performed for different fan levels. States between unloaded state (30%) and max. fan level (100%) are described in the following table. Measurements of the sound intensity are performed in accordance to DIN EN ISO 9614-2. Valid for empty Chassis only.

| Fan Level | Sound Power L <sub>WA</sub> | Sound Pressure L <sub>PA</sub> | Sound Pressure L <sub>PA</sub> |

|-----------|-----------------------------|--------------------------------|--------------------------------|

| [%]       | [dB(A)]                     | [dB(A)]                        | [dB(A)]                        |

|           |                             | 0,2m distance                  | 1,0m distance                  |

| 100       | 71,1                        | 70,6                           | 59,3                           |

| 90        | 70,9                        | 69,7                           | 58,3                           |

| 80        | 69,4                        | 68,2                           | 57,0                           |

| 70        | 67,8                        | 66,6                           | 55,4                           |

| 60        | 65,7                        | 64,7                           | 53,3                           |

| 50        | 63,4                        | 62,4                           | 51,0                           |

| 40        | 60,2                        | 59,6                           | 47,8                           |

| 30        | 56,7                        | 56,1                           | 44,3                           |

Table 5: Acoustic Emission

For information about testing procedure and evaluated data contact your local sales partner.

#### 4.9 Mechanical

### 4.9.1 Materials

#### **Base Materials:**

Sheet Aluminium(AW-5754-H22)Extruded Aluminium(EN-AW-6060 T66)Plate Aluminium(EN-AW-5005A-H12)Aluzink Coated(Low Carbon Steel AISI 1008 ASTMA619)Polycarbonate LexanPolyethylene Foam

#### Finishes:

Color passivated Clear passivated Clear anodized Polyester powder poated Powder coated fine texture Painted fine texture

#### 4.9.2 Dimensions

Figure 16: Dimensions Front View

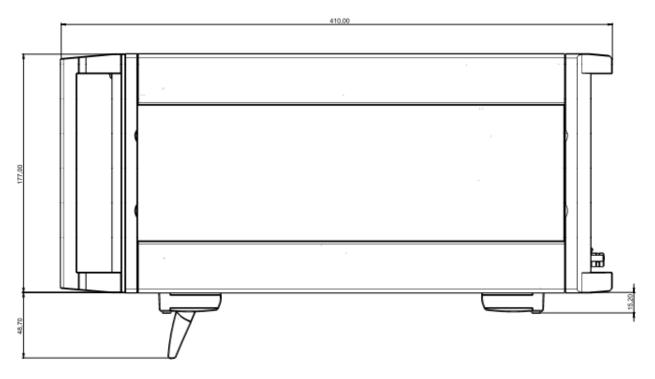

#### Figure 17: Dimensions Side View

#### Figure 18: Dimensions Rear View

# 5 System Status

#### 5.1 Indicator LED

The power switch on the front of the chassis has two integrated LEDs (red and white). CMM signals FRONT\_LED\_RD and FRONT\_LED\_WT are used to indicate the chassis status via both of these LEDs. Table below shows the chassis states and corresponding LED behavior.

Table 6: System Status Indicator LED

| Chassis state                             | Indicator LED  | LED_WT level | LED_RD level |

|-------------------------------------------|----------------|--------------|--------------|

| Chassis is off                            | Both LED OFF   | LOW          | LOW          |

| Chassis powered<br>and operating properly | Solid white    | HIGH         | LOW          |

| air intake temperature<br>is above 55°C   | Flashing white | Pulse        | LOW          |

| One of the chassis fans failed            | Solid red      | LOW          | HIGH         |

| System voltages out of limits             | Flashing red   | LOW          | Pulse        |

#### 5.2 Fan Modes

Upon the application requirement you can choose either for autonomous fan control or maximum air volume throughput for optimized and remote environments.

AUTO (def): Fan Level controlled according to sensor temperature MAX: Fan PWM set to 100%, Fans run at max. speed FAN SPEED

### 5.3 Power / Inhibit Modes

The power-on behavior depends on the setting of the inhibit mode switch at the rear panel. When the inhibit mode switch is set to "**DEF**", the push button controls the power supply outputs. By pushing the power button at the front side the chassis will start and shut down according to ATX PSU specification 3.2.1.0. When the inhibit mode switch is set to '**MAN**', the chassis boots when AC-power is applied, as long as Inhibit (Pin 5 at the rear DSUB connector) is not connected to GND, please refer to 5.4.

| Please note the following:                                                              |

|-----------------------------------------------------------------------------------------|

| In order to ensure a proper function of the <b>DEF</b> and <b>MAN</b> setting, the BIOS |

| settings of the used controller should be adjusted.                                     |

| DEF Mode:                                                                               |

| - Set BIOS Power Loss Control to "Remain Off".                                          |

| MAN Mode:                                                                               |

| - Set BIOS Power Loss Control to "Turn On".                                             |

#### 5.4 External Interfaces

#### CLK10\_IN

A BNC rear connector is located at the rear panel and can be used for external clock source input. All chassis clock correlations will follow the external source after the glitch free resourcing. For more information please see chapter 6.3

#### CLK10\_OUT

Another BNC rear connector is located at the rear panel and can be used for clock 10 MHz output. For more signal characteristics please see chapter 6.2

#### DSUB Connector "Voltage Monitor"

All active system voltages are present at a rear 9pin DSUB connector and can be used for external measurements. With the implementation of the INHIBIT signal multiple chassis applications can be daisy-chained for synced Power-On Behavior.

Whenever the chained **INHIBIT**-Pin is attached to GND potential, System voltages of attached Chassis will be shut down immediately. When **INHIBIT**-Pin is released and Inhibit Mode is set to "**MAN**" system voltages and chassis will power up again.

|             | Pin | Signal                  | Pin | Signal                  |

|-------------|-----|-------------------------|-----|-------------------------|

|             | 1   | GND                     | 6   | +12V (via 10k resistor) |

|             | 2   | +5V0 (via 10k resistor) | 7   | not used                |

| 5           | 3   | not used                | 8   | -12V (via 10k resistor) |

|             | 4   | +3V3 (via 10k resistor) | 9   | GND                     |

| VOLTAGE MON | 5   | INHIBIT                 |     |                         |

Table 7: DSUB Connector "Voltage Monitor"

# 6 Timing and Trigger Functions

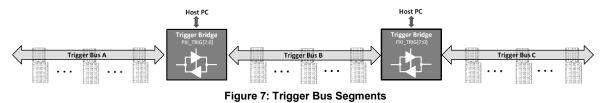

### 6.1 Trigger and Segments

Figure 19: Trigger Bus Segments

The PXIe chassis trigger bus is divided into 3 isolated trigger bus segments with 8 trigger lines each X\_PXI\_TRIG[0:7].

- Trigger segment I covers slot 1 through 6

- Trigger segment II covers slot 7 through 12

- Trigger segment III covers slot 13 through 18

Through the PXI trigger bridges, each trigger line of a segment can be individually routed in each direction to the according signal of an neighbored trigger segment or be left isolated.

The trigger bridges are controlled by the chassis management and can be set by SCHROFF Software Tooling (see <u>chapter 3.5</u>) or direct I2C/SMBus Access (see <u>chapter 7.3.5</u>).

#### 6.2 CLK10, CLK100 parameters

|  |   | 1 |

|--|---|---|

|  | 1 |   |

|  |   |   |

|  |   |   |

For all specifications not mentioned in the tables below refer to the PXI-1 und PXI-5 PXIe Hardware specification.

#### Table 8: PXI\_CLK10

| PXI_CLK10                      |                                                                                                      |

|--------------------------------|------------------------------------------------------------------------------------------------------|

| Maximum slot to slot time skew | 500 ps<br>Note: PXI-5 spec specifies 1 ns                                                            |

| Frequency accuracy             | ±25 ppm max (guaranteed over the operating temperature range)<br>Note: PXI-5 spec specifies ±100 ppm |

| Maximum jitter                 | 5 ps RMS phase jitter (10 Hz 1 MHz range)                                                            |

| Duty cycle                     | 45 % to 55 %                                                                                         |

| Unloaded signal swing          | 3.3 V ±0.3 V (LVCMOS driver)                                                                         |

#### Table 9: PXIe\_CLK100

| PXIe_CLK100                                                                                                                |                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Maximum slot to slot time skew                                                                                             | 80 ps<br>Note: PXI-5 spec specifies 200 ps                                                           |

| Frequency accuracy                                                                                                         | ±25 ppm max (guaranteed over the operating temperature range)<br>Note: PXI-5 spec specifies ±100 ppm |

| Maximum jitter                                                                                                             | 5 ps RMS phase jitter (10 Hz – 12 kHz, 12 kHz – 20 MHz range)                                        |

| Duty cycle                                                                                                                 | 45 % to 55 %                                                                                         |

| Absolute differential voltage when each line pair is terminated with a 50 $\Omega$ load to 1.30 V (or Thevenin equivalent) | 500 mV to 950 mV (LVPECL driver)                                                                     |

Values above valid for nVent SCHROFF PXIe standard products. Optimized parameters are available on request (Jitter ≤1 ps, Accuracy 2 ppm, slot-to-slot skew 100 ps)

#### Table 10: External 10 MHz Reference In

| External 10 MHz Reference In             |                                              |  |  |  |  |  |

|------------------------------------------|----------------------------------------------|--|--|--|--|--|

| Frequency                                | 10 MHz ±100 ppm                              |  |  |  |  |  |

| Input amplitude                          | 200 mV to 5 V, square wave or sine wave      |  |  |  |  |  |

| Maximum jitter introduced by backplane   | 1 ps RMS phase jitter (10 Hz – 10 MHz range) |  |  |  |  |  |

| Rear panel BNC connector input impedance | 50 Ω ±5 Ω                                    |  |  |  |  |  |

#### Table 11: External 10 MHz Reference Out

#### External 10 MHz Reference Out

| Frequency accuracy    | 10MHz ±25 ppm max.                                |

|-----------------------|---------------------------------------------------|

|                       | (guaranteed over the operating temperature range) |

| Maximum jitter        | 5 ps RMS phase jitter (10 Hz – 1 MHz range)       |

| Unloaded signal swing | 3.3V ± 0.3V (LVCMOS driver)                       |

| Output impedance      | 50 Ω ±5 Ω                                         |

#### 6.3 Clock Source Selection

When a 10 MHz reference clock is present at the System Timing Slot or the external panel connector CLK10\_IN, PXI\_CLK10, PXIe\_CLK100 and PXIe\_SYNC100 are phase-locked to this reference clock signal:

| Mode | System Timing Slot      | External CLK10_IN       | Backplane Clock Module                                                                                                                |

|------|-------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1    | 10 MHz clock<br>present | 10 MHz clock<br>present | External CLK10_OUT, PXI_CLK10, PXIe_CLK100 and PXIe_SYNC100 are phase-locked to reference clock signal from <b>System Timing Slot</b> |

| 1    | 10 MHz clock<br>present | -                       | External CLK10_OUT, PXI_CLK10, PXIe_CLK100 and PXIe_SYNC100 are phase-locked to reference clock signal from System Timing Slot        |

| 2    | -                       | 10 MHz clock<br>present | External CLK10_OUT, PXI_CLK10, PXIe_CLK100 and PXIe_SYNC100 are phase-locked to reference clock signal from External CLK10_IN         |

| 3    | -                       | -                       | External CLK10_OUT, PXI_CLK10, PXIe_CLK100 and PXIe_SYNC100 are generated internally by the Clock Module Reference Clock              |

Table 12: Clock Source Selection

The source for the reference signal is selected automatically by that default priority order. If no external clock source is present the clock module will generate the required timing signals based on its own source.

#### 6.4 SYNC\_CTRL Behavior

The Chassis Management allows to modify the signal "PXIe\_SYNC100" behavior by changing the value of "SynDiv" register (see chapter 7.3.6).

#### PXIe\_SYNC100 Modes

- When "SynDiv" register is set to n=2...255, the resulting PXIe\_SYNC100 frequency is  $PXIe_SYNC100_{new} = \frac{10 \text{ MHz}}{n}$  and the PXIe\_SYNC\_CTRL signal works as a PXIe\_SYNC100 restart initialization (see PXI-5 chapter 4.4.1.4).

- When "SynDiv" register is set to n=0, the PXIe\_SYNC100 frequency is 10 MHz and the PXIe\_SYNC\_CTRL signal works as PXIe\_SYNC100 Enable (see PXI-5 chapter 4.4.1.4).

- When "SynDiv" is set to n=1, the PXIe\_SYNC100 frequency is 10 MHz and the PXIe\_SYNC\_CTRL is deactivated.

## 7 SCHROFF Chassis Management

The nVent SCHROFF PXIe Chassis Management allows access from the operating system directly to all important chassis functions. The Chassis Management Module (CMM) provides an I2C/SMBus interface which is connected to backplane SMB (system slot pins XP3-a3, -b3).

The Chassis Management features:

- Monitors all chassis voltage levels and chassis temperatures

- Monitors and control the power supply and fans

- Controls SYNC100 features from clock module

- Controls the configuration of PXI trigger bridges

- Controls the chassis status LED

The CMM provides access to all important chassis functions (voltage monitor, FAN settings, temperature monitor, Trigger bridge settings, PXIE\_SYNC100 frequency settings ...). The status of chassis functions can be monitored/changed by access corresponding register settings.

#### 7.1 I2C/SMBus interface description

The CMM provides a <u>primary</u> I2C/SMBus interface connected to the SMB (system slot pins XP3-a3, -b3 and peripheral slots). This Interface allows the host operating system to directly access all important chassis functions. On a decoupled secondary side the CMM interacts with module internal I2C interface, sensors and monitoring.

#### 7.2 I2C Address

PXI-5 specification chapter 4.8 defines an I2C address range for chassis-specific functions. Allowed addresses are:

| 58h = 0101 1000b |  |

|------------------|--|

| 5Ah = 0101 1010b |  |

| 5Ch = 0101 1100b |  |

(used as default CMM address)

The CMM's address can be changed to above allowed addresses upon request. Please get into contact with your local sales representative.

### 7.3 Register map:

Chapters below describe the CMM registers and their functions.

| Table 13: CMM | Register | Overview |

|---------------|----------|----------|

|---------------|----------|----------|

| Registe<br>[Start | r Range<br>/ End] | Description            | see sub-chapter |

|-------------------|-------------------|------------------------|-----------------|

| 0x00              | 0x09              | Voltage Monitoring     | <u>7.3.1</u>    |

| 0x0E              | 0x14              | Power Control          | <u>7.3.2</u>    |

| 0x19              | 0x28              | Fan Control            | <u>7.3.3</u>    |

| 0x2C              | 0x30              | Temperature Monitoring | <u>7.3.4</u>    |

| 0x34              | 0x3C              | Trigger Bridge Control | <u>7.3.5</u>    |

| 0x45              | 0x48              | Clock Control          | <u>7.3.6</u>    |

| 0x50              | 0x58              | CMM Software Revision  | <u>7.3.7</u>    |

#### 7.3.1 Voltage monitor registers

#### Table 14: CMM Voltage monitor registers

| Register<br>address | Name     | Description                      | Direction  |  |

|---------------------|----------|----------------------------------|------------|--|

| 0x00                | 5VauxMSB | 5 Vaux voltage level (1bit = mV) | Read only  |  |

| 0x01                | 5VauxLSB |                                  | Read only  |  |

| 0x02                | 3V3MSB   | 3V3 voltage level (1bit = mV)    | Read only  |  |

| 0x03                | 3V3LSB   |                                  | Read Only  |  |

| 0x04                | 5VMSB    | 5 V voltage level (1bit = mV)    | Read only  |  |

| 0x05                | 5VLSB    | 5 V Voltage level (Tbit – TTV)   | iteau only |  |

| 0x06                | +12VMSB  | +12 V voltage level (1bit = mV)  | Road only  |  |

| 0x07                | +12VLSB  |                                  | Read only  |  |

| 0x08                | -12VMSB  | -12 V voltage level (1bit = mV)  | Read only  |  |

| 0x09                | -12VLSB  |                                  | Read only  |  |

### 7.3.2 Power control registers

| Table 15: | СММ   | Power   | control  | reaisters |

|-----------|-------|---------|----------|-----------|

|           | 0.000 | 1 01101 | 00110101 | registers |

| Register<br>address | Name         | Description                                                                                                                                                                                                   | Direction |

|---------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 0x0E                | SEL_SS_PS_ON | Shows the current level of CMM input for<br>"PS_ON" source selection slider.<br>Value = 0: signal "EXT_PS_ON_IN" is<br>used as "PS_ON" source<br>Value > 0: signal "SS_PS_ON_IN" is used<br>as "PS_ON" source | Read only |

| 0x0F                | SS_PS_ON_IN  | Shows the current level of CMM input for<br>"PS_ON" signal from system slot<br>Value = 0: received signal is LOW<br>Value > 0: received signal is HIGH                                                        | Read only |

| 0x10                | EXT_PS_ON_IN | Shows the current level of CMM input for<br>"PS_ON" signal from external source.<br>Value = 0: received signal is LOW<br>Value > 0: received signal is HIGH                                                   | Read only |

| 0x11                | PS_ON_OUT_1  | Shows the current state of the CMM output<br>"PS_ON_1"<br>Value = 0: output set LOW<br>Value > 0: output set HIGH                                                                                             | Read only |

| 0x12                | PS_ON_OUT_2  | Shows the current state of the CMM output<br>"PS_ON_2"<br>Value = 0: output set LOW<br>Value > 0: output set HIGH                                                                                             | Read only |

| 0x13                | PS_ON_OUT_3  | Shows the current state of the CMM output<br>"PS_ON_3"<br>Value = 0: output set LOW<br>Value > 0: output set HIGH                                                                                             | Read only |

| 0x14                | PS_ON_OUT_4  | Shows the current state of the CMM output<br>"PS_ON_4"<br>Value = 0: output set LOW<br>Value > 0: output set HIGH                                                                                             | Read only |

### 7.3.3 Fan control registers

| Table  | 16: | СММ | Fan | control | registers |

|--------|-----|-----|-----|---------|-----------|

| 1 4010 |     | •   |     | 001101  | regiotore |

| Register<br>address | Name                 | Description                                                 | Direction     |

|---------------------|----------------------|-------------------------------------------------------------|---------------|

|                     |                      | 0 = CMM controls the fan speed                              | Read / write  |

|                     |                      | 1 = embedded controller (system slot card)                  |               |

|                     |                      | controls the fan speed.                                     |               |

| 0x19                | Remote               | This register must be written each 10                       |               |

| 0.10                |                      | seconds with '1' by system controller to stay               |               |

|                     |                      | in Remote control mode, otherwise the                       |               |

|                     |                      | CMM folds back to autonomous mode.                          |               |

|                     |                      | Default value: 0                                            |               |

|                     |                      | Sets required fan speed for all fans in %                   | Read / write  |

| 0x1A                | SetFAN               | (0h = min fan speed, 0x64h = 100% = max                     |               |

|                     |                      | fan speed, in remote control only).                         |               |

|                     |                      | Default value: 0x64 = 100%                                  |               |

|                     |                      | Valid in autonomy mode only                                 | Read / write  |

| 0x1B                | FAN_curve            | Fan curve setting                                           | (value stored |

| UNID                |                      | Default value: last setting stored in internal              | in EEPROM)    |

|                     |                      | EEPROM, factory value = 0x05                                |               |

| 0x1C                | FAN_Tacho_1_HighByte |                                                             | Read only     |

| 0x1D                | FAN_Tacho_1_LowByte  |                                                             |               |

| 0x1E                | FAN_Tacho_2_HighByte | Shows the fan rotation speed.                               |               |

| 0x1F                | FAN_Tacho_2_LowByte  | Value in RPM                                                |               |

| 0x20                | FAN_Tacho_3_HighByte |                                                             |               |

| 0x21                | FAN_Tacho_3_LowByte  |                                                             |               |

| 0x22                | FAN_Tacho_4_HighByte |                                                             |               |

| 0x23                | FAN_Tacho_4_LowByte  |                                                             |               |

| 0x28                | CMM_FAN_ready        | Shows that the fans are initialized and ready for operation |               |

#### 7.3.4 Temperature monitor registers

| Register<br>address | Name             | Description                                                                             | Direction |

|---------------------|------------------|-----------------------------------------------------------------------------------------|-----------|

| 0x2C                | TEMP_AIR_inlet   | Chassis inlet air temperature<br>sensor. Values and resolution see<br>description below | Read only |

| 0x2D                | TEMP_AIR_outlet1 | Chassis outlet sensor 1. Values<br>and resolution see description<br>below              | Read only |

| 0x2E                | TEMP_AIR_outlet2 | Chassis outlet sensor 2. Values<br>and resolution see description<br>below              | Read only |

| 0x2F                | TEMP_AIR_outlet3 | Chassis outlet sensor 3. Values<br>and resolution see description<br>below              | Read only |

| 0x30                | TEMP_AIR_outlet4 | Chassis outlet sensor 4. Values<br>and resolution see description<br>below              | Read only |

Measurement range is defines from 0°C to +80°C

Resolution for all temperature sensors is 1 Kelvin per bit.

Bit [7:0] = temperature value

Examples:

| TEMP_AIR_x<br>Value bin | TEMP_AIR_x<br>Value hex | Temperature |

|-------------------------|-------------------------|-------------|

| 0011 0011b              | 33h                     | +51°C       |

| 0010 0000b              | 20h                     | +32°C       |

| 0001 0011b              | 13h                     | +19°C       |

| 0000 0000b              | 0h                      | +0°C        |

#### 7.3.5 Trigger bridge control registers

| Register<br>address | Name   | Description                                                                  | Direction                        |

|---------------------|--------|------------------------------------------------------------------------------|----------------------------------|

| 0x34                | TBPres | Trigger bridge present; shows the availability of individual trigger bridges | Read only                        |

| 0x35                | TB1EN  | Enables and disables the trigger bridge 1 drivers                            |                                  |

| 0x36                | TB1Dir | Sets the direction of the drivers on trigger bridge 1                        |                                  |

| 0x37                | TB2EN  | Enables and disables the trigger bridge 2 drivers                            |                                  |

| 0x38                | TB2Dir | Sets the direction of the drivers on trigger bridge 2                        | Read / write<br>(value stored in |

| 0x39                |        | Enables and disables the trigger                                             | EEPROM)                          |

bridge 3 drivers

trigger bridge 3

bridge 4 drivers

trigger bridge 4

#### Table 18: CMM Trigger bridge control registers

TBPres: Trigger bridge present register:

TB3EN

TB3Dir

TB4EN

TB4Dir

0x3A

0x3B

0x3C

|                                     | 00 .         |          | 3    |      |          |          |          |          |

|-------------------------------------|--------------|----------|------|------|----------|----------|----------|----------|

| Bit                                 | 7            | 6        | 5    | 4    | 3        | 2        | 1        | 0        |

| function                            | Not          | Not      | Not  | Not  | Trigger  | Trigger  | Trigger  | Trigger  |

|                                     | used         | used     | used | used | Bridge 4 | Bridge 3 | Bridge 2 | Bridge 1 |

|                                     |              |          |      |      | present  | present  | present  | present  |

| value                               | 0            | 0        | 0    | 0    | Х        | Х        | Х        | Х        |

| X = 0: Trigger bridge not available |              |          |      |      |          |          |          |          |

| X = 1: Trigger bridge available     |              |          |      |      |          |          |          |          |

| Default va                          | lue: not app | olicable |      |      |          |          |          |          |

Sets the direction of the drivers on

Enables and disables the trigger

Sets the direction of the drivers on

#### TBnEN<sup>1</sup>: Trigger bridge enable register:

| Bit                                   | 7       | 6       | 5       | 4       | 3       | 2      | 1        | 0       |

|---------------------------------------|---------|---------|---------|---------|---------|--------|----------|---------|

| function                              | PXI_TRI | PXI_TRI | PXI_TRI | PXI_TRI | PXI_TRI | PXI_TR | PXI_TRIG | PXI_TRI |

|                                       | G7_EN   | G6_EN   | G5_EN   | G4_EN   | G3_EN   | IG2_EN | 1_EN     | G0_EN   |

| value                                 | Х       | Х       | Х       | Х       | Х       | Х      | Х        | Х       |

| X = 0: Trigger bridge driver disabled |         |         |         |         |         |        |          |         |

<sup>&</sup>lt;sup>1</sup> n = trigger bridge number 1 to 4

X = 1: trigger bridge driver enabled

Default value: last settings stored in internal EEPROM, factory value = 0x00

|                                                                                                      | 00      | 0      | 0      |        |         |         |         |        |

|------------------------------------------------------------------------------------------------------|---------|--------|--------|--------|---------|---------|---------|--------|

| Bit                                                                                                  | 7       | 6      | 5      | 4      | 3       | 2       | 1       | 0      |

| function                                                                                             | PXI_TRI | PXI_TR | PXI_TR | PXI_TR | PXI_TRI | PXI_TRI | PXI_TRI | PXI_TR |

|                                                                                                      | G7_D    | IG6_D  | IG5_D  | IG4_D  | G3_D    | G2_D    | G1_D    | IG0_D  |

| value                                                                                                | Х       | Х      | Х      | Х      | Х       | Х       | Х       | Х      |

| X = 0: bridge sends trigger signals from left to right (from lower to higher backplane slot numbers) |         |        |        |        |         |         |         |        |